- 您现在的位置:买卖IC网 > Sheet目录1993 > DS1338C-33#T&R (Maxim Integrated Products)IC RTC 56BYTE NV SRAM 16SOIC

DS1338 I2C RTC with 56-Byte NV RAM

5 of 16

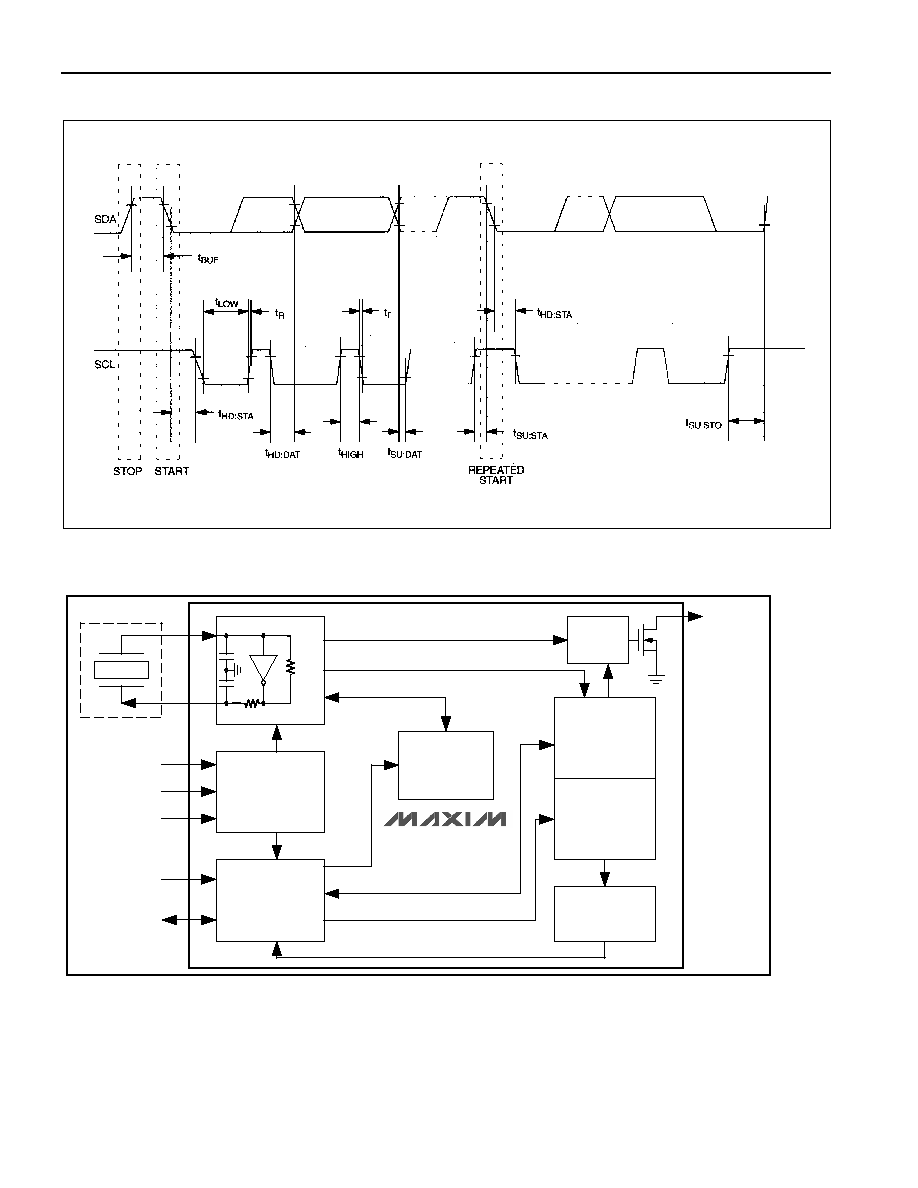

Figure 2. Timing Diagram

Figure 3. Block Diagram

RAM

(56 X 8)

SERIAL BUS

INTERFACE

AND ADDRESS

REGISTER

CONTROL

LOGIC

1Hz

1Hz/4.096kHz/8.192kHz/32.768kHz

MUX/

BUFFER

USER BUFFER

(7 BYTES)

CLOCK,

CALENDAR,

AND CONTROL

REGISTERS

"C" VERSION ONLY

POWER

CONTROL

DS1338

X1

C

L

CL

X2

SDA

SCL

SQW/OUT

V

CC

GND

V

BAT

Oscillator

and divider

N

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DS1339AU+

IC RTC I2C W/ALARM 8USOP

DS1339C-2#

IC RTC I2C W/ALARM 16-SOIC

DS1340Z-33/T&R

IC RTC I2C W/CHARGER 3.3V 8-SOIC

DS1340Z-3

IC RTC I2C W/CHARGER 3V 8-SOIC

DS1341T+

IC RTC I2C W/ALARM 6TDFN-EP

DS1344D-33+

IC RTC SPI 3.3V 14TDFN-EP

DS1347T+

IC RTC/CALENDAR SPI 8TDFN

DS1371U+C01

IC BINARY COUNTER 32-BIT 8-USOP

相关代理商/技术参数

DS1338C-33+

制造商:Maxim Integrated Products 功能描述:REAL TIME CLOCK SERL 56BYTE 16SOIC - Bulk

DS1338U-18

功能描述:实时时钟 I2C Serial RTC w/56 Byte NV RAM RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1338U-18+

功能描述:实时时钟 I2C Serial RTC w/56 Byte NV RAM RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1338U-18+T&R

制造商:Maxim Integrated Products 功能描述:SERIAL RTC 8PIN USOP 1.8V T&R - Tape and Reel 制造商:Maxim Integrated Products 功能描述:IC RTC 56BYTE NV RAM 1.8V 8-USOP

DS1338U-3

功能描述:实时时钟 I2C Serial RTC w/56 Byte NV RAM RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1338U-3/T&R

制造商:Maxim Integrated Products 功能描述:REAL TIME CLOCK SERL 56BYTE 8USOP - Tape and Reel

DS1338U-3+

功能描述:实时时钟 I2C Serial RTC w/56 Byte NV RAM RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1338U-3+T&R

制造商:Maxim Integrated Products 功能描述:REAL TIME CLOCK SERL 56BYTE 8USOP - Tape and Reel 制造商:Maxim Integrated Products 功能描述:IC RTC 56BYTE NV RAM 3V 8-USOP